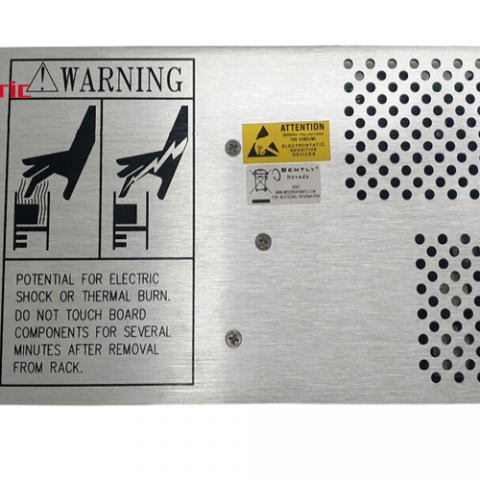

BENTLY 3500/60 163179-01 Temperature module

BENTLY 3500/60 163179-01 By writing “0” to the appropriate “timer”, it is possible to clear specific timer interrupts x caused by the IRQ “field. Alternatively, writing the appropriate timer x IRQ Clear (TxIC) register will also clear the interrupt. When using the “Raise IRQ when Timer x” field to clear interrupts, note that it is important to ensure that the correct bitmask is used so that other register Settings are not affected.

The preferred clearing method interrupts using the “timer x IRQ Clear” register described on page 52. BENTLY 3500-60 163179-01 Timer Control Status Register 2 (TCSR2) The timer is also controlled by bits in Timer Control Status register 2 (TCSR2) located at the offset 0x04 of the address in BAR2.

The mapping register for the bits in this field is as follows: The “Read latch selection” bit is used to select a latch-mode timer for programmable memory. If this bit is set to “0”, each timer output is latched to its address when either is read. For example, a read of the TMRCCR12 register latches timers 1 and 2. Count of the read latch timer 3 of the TMRCCR3 register. Each read of any of these registers continues. This subsequent reading of the TMRCCR3 and TMRCCR4 registers does not latch the new count value, allowing the count of all timers in the same time instance to be obtained.

There are no reviews yet.